抽象分层

常规的抽象分层方式:可以用Y-Chart图来表示,分为三个域:行为域,行为域看不见几何信息与结构信息,它定义输入与输出来描述响应,使得复杂模块可重复利用,大规模设计成为可能;结构域:看不见几何结构、尺寸信息,它通过基本部件(逻辑门与触发器)互连表述,能看见基本部件之间的逻辑结构。注重实体内部逻辑结构。不考虑实体物理实现。简单设计,结构域表示可替代行为域表示。几何域:定每个基本部件在硅片中尺寸信息、位置信息、部件间物理互连信息。

常规的分层方法将整个集成电路设计分作系统层级、模块层级、门电路层级、电路层级、器件层级共五个层级。

意义:提高集成电路的设计效率,使得单个设计人员可以更快速的完成更大规模的电路设计。实现从系统到模块的层次化、精细化的任务分工。产业链可以充分借助高性能机器、EDA工具实现按规则的优化迭代。设计者可更多聚焦到特定边界下的极致任务高效优化。

什么是SSN?如何避免或降低寄生电感引起的同步开关噪声(SSN)引起的地弹和电源反弹的影响?

SSN:当器件处于开关状态,产生瞬间变化的电流di/dt,在经过回流途径上存在的电感时,形成交流压降,从而引起噪声

地弹:由于封装电感而引起地平面的波动,造成芯片和系统地不一致

电源反弹:由于封装电感而引起芯片和系统电源差异

降低影响:(1)增加去耦电容(2) 使消耗大电流的翻转不同时发生(3) 采用先进的封装技术,因为可以大大减小寄生电感 (4)增加片外信号的上升/下降时间:减小了瞬态电流 (5) I/0 压焊块和芯片内核有各自的电源引线

CMOS反相器

CMOS反相器参数: - 成本:用复杂性和面积来看看;完整性:完整性和稳定性;性能:由动态(瞬态)响应决定;能效:由能耗的功耗决定

降低反相器尺寸的意义:MOSFET的尺寸变小意味著栅极面积减少,如此可以降低等效的栅极电容,从而降低延迟。

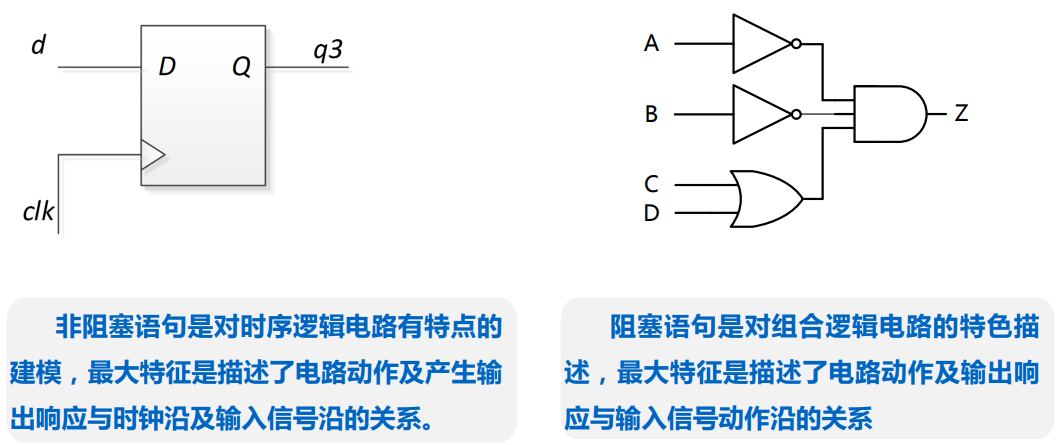

阻塞赋值与非阻塞赋值

阻塞赋值:值时先计算=右手部分的值,此时赋值语句不允许任何别的verilog语句干扰,完成当前赋值后,允许别的赋值语句的执行;

非阻塞赋值:赋值操作时刻开始计算<=右边的表达式;赋值操作结束时刻,更新左边的值,在计算右边表达式和更新左边值期间,允许其他语句操作。

电路抽象要点:

编程要点:时序电路结构建模,采用非阻塞赋值;锁存器电路建模,采用非阻塞赋值;用always块建立组合逻辑模型时,用阻塞赋值;在同一个always块中建立时序和组合逻辑电路时,用非阻塞赋值;在同一个always块中,不要既用非阻塞,又用阻塞赋值;不要再同一个以上的always块中为同一个变量赋值赋值时,不要使用#0延迟。

三态门

三态缓冲器区分内部外部

-内部三态缓冲器逻辑(需要设备内的三态缓冲器)

-外部三态缓冲逻辑(在I/O引脚处需要一个三态缓冲)

ASIC/FPGA如何提供三台缓冲器

-ASIC/FPGA将使用MUX实现内部三态缓冲器

-所有的I/O焊盘都可以提供真正的三态缓冲器

状态机

一段式状态机特点:用一个always块来描述状态机,在该模块中既描述状态转移,又描述状态的输入和输出;对于大型状态机,这种方法维护难度大;

两段式状态机特点:用两个always块来描述状态机,一个always模块采用同步时序描述状态转移,一个模块采用组合逻辑判断状态转移条件,描述状态转移规律以及输出;

三段式状态机特点:用三个always块来描述状态机,第一个时序逻辑always块用来描述当前状态,(current state)寄存器的复位和变化,第二个组合always描述下一状态的转移(next state logic),第三个always组合状态输出(可以用组合电路输出,也可第以时序电路输出。适合大型状态机,可综合设计,易于修改错误。

补码

原码转换补码:正数不变;负数除符号位外取反加一,或2的n次方-|x|,例如-128的补码等于2的8次方-128.

补码的优点

- 补码的减法运算可以转换为补码的加法运算

- 无符号数和有符号数的加法运算可用同一电路完成,只要结果不超过表示范围/不溢出

- 负数补码的转换可以用求补运算实现

补码运算溢出

- 表示范围-2的n-1次方--2的n-1次方-1,超出该范围就会溢出。

- 如果次高位向最高位进位(或借位)而最高位向前无进位(或借位),则溢出

- 如果次高位无向最高位进位(或借位),而最高位向前有进位(或借位),则溢出

串行进位加法器:

结构:由N个一位全加器串联而成,第i级用来产生第i+1级的和

特点:结构直观简单,运行速度慢

超前进位加法器

原理:利用进位产生项和进位传播项实现加法操作从而避免串行进位链中的进位逐级传播,从而大大加快运算速度,代价是电路复杂度上升,以空间换时间。

浮点数的表示方式

单精度32bit:1bit sign,8bits E,23bits P(AND 1bit hidden,实际上尾数有24bit)

浮点数加法

- 统一exponent对阶

- 尾数significant相加

- 归一化

浮点数乘法

- 指数相加

- 尾数相乘

- 归一化

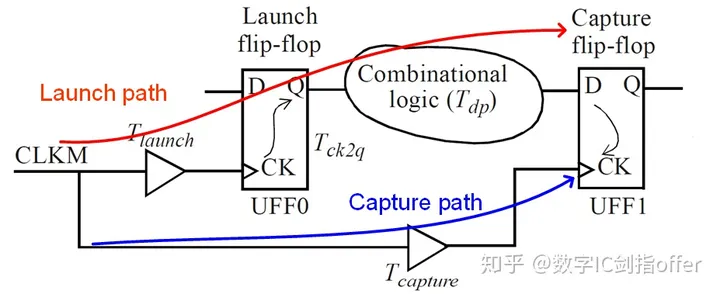

时序路径需要满足的条件

- Setup:Tctq + Tpath < Tclk - Tskew - Tsetup

- Hold:Tctq + Tpath > Thold + Tskew

setup违例可以通过降频消除而hold违例与频率无关。结合经典时序电路模型图理解。

Memory分级

- 1cycle:Register File寄存器堆 / L1 Cache(SRAM)

- 5-10cycle:L2 Cache(SRAM)

- 20-30cycle:DDR

- Hundreds cycle:Hard Disk

降低Cache Miss的方法

- 冷启动阶段,不可避免地经过一系列cache miss,这一阶段的miss基本上无法降低。

- conflict miss:增加组相连数

- capaci miss:增加cache总体大小

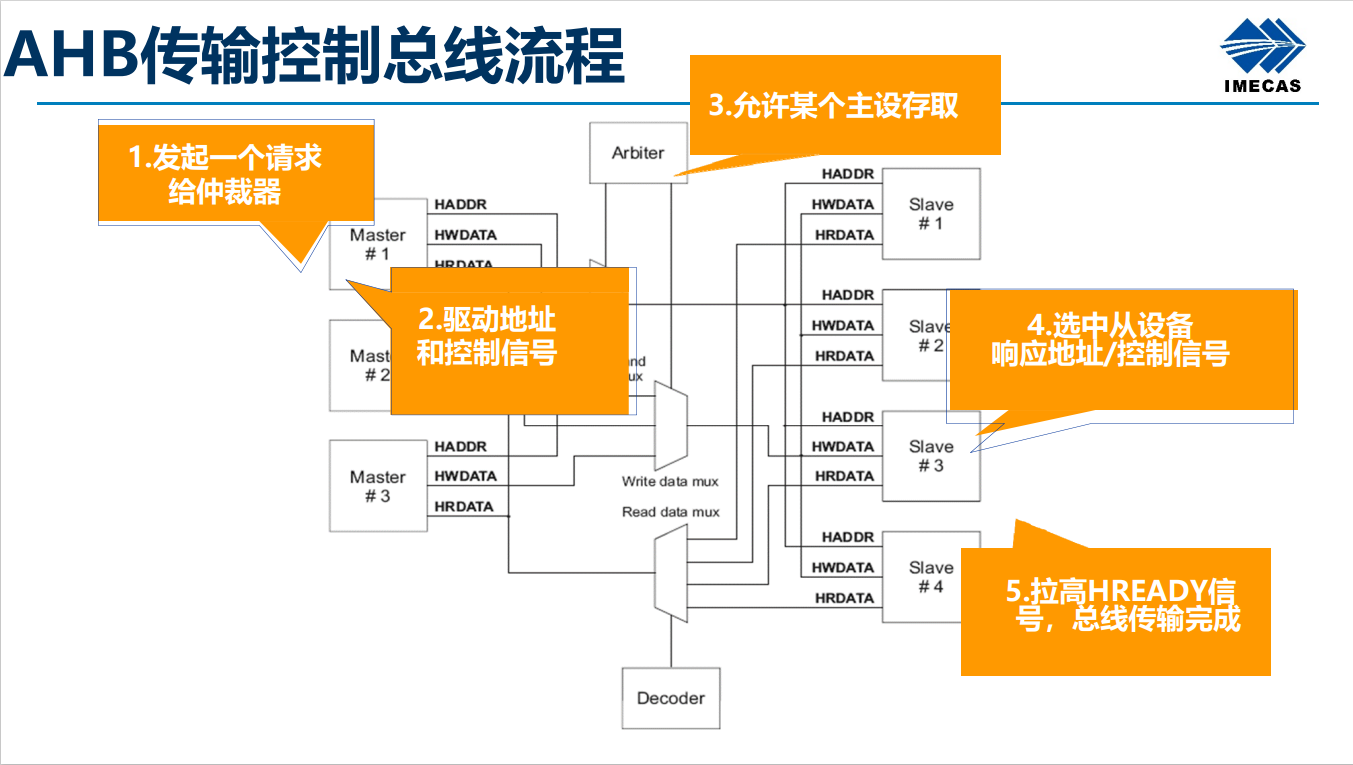

AHB传输控制总线流程

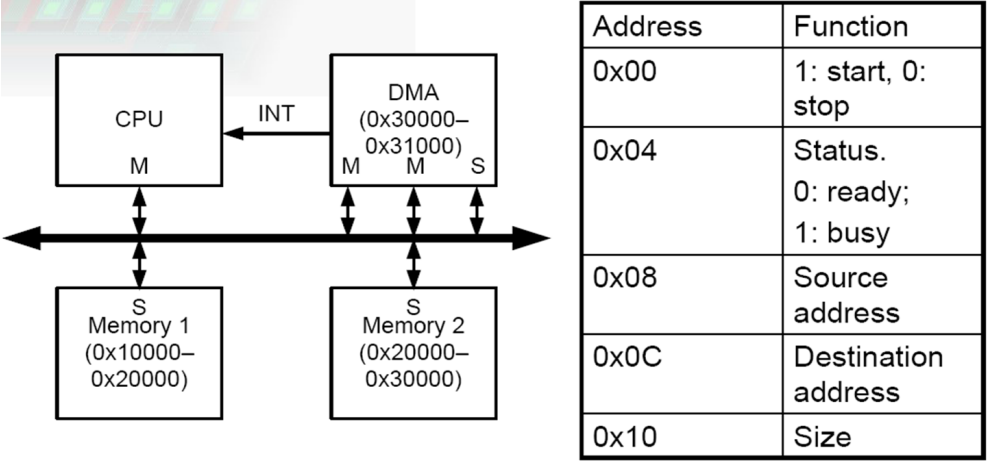

DMA工作流程

假设DMA相关的寄存器地址如下表所示

那么

Step1:CPU检查0x04处DMA的状态是否Busy

Step2:CPU向0x08、0x0C、0x10处写入源地址、目标地址、以及传输大小。

Step3:CPU向0x00写入Start Flag

Step4:DMA搬运数据

Step5:DMA传输完毕向CPU发出一个中断请求

Step6:CPU检查0x04处DMA的状态

DRAM的刷新

不管是哪一种动态RAM,都是利用电容存储电荷的原理来保存信息的,由于电容会逐渐放电,所以,对动态RAM必须不断进行读出和再写入,以使泄放的电荷受到补充,也就是进行刷新。

动态MOS存储器采用“读出”方式进行刷新, 先将原存信息读出,再由刷新放大器形成原信息并重新写入。

- (1) 刷新周期 从上一次对整个存储器刷新结束到下一次对整个存储器全部刷新一遍为止,这一段时间间隔叫 刷新周期。一般为2ms, 4ms, 8ms。

- (2) 刷新方式 常用的刷新方式有三种: 集中式、分散式、异步式。

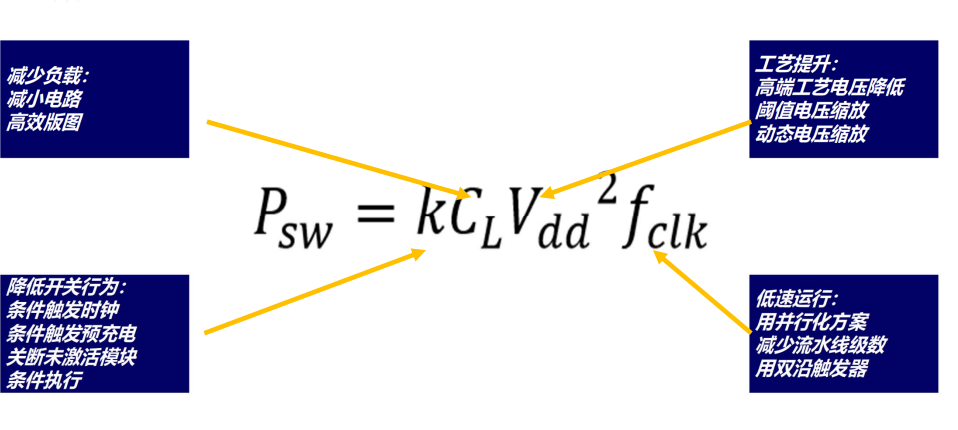

低功耗的基本理论

芯片的功耗分为开关功耗和短路功耗,作为设计者我们主要关注开关功耗。

低功耗设计常用技术

时钟关断 (Clock-Gating)

多域值电压库(Multi-threshold libraries)

多电压(Multi-Voltage)

电源关断 (Power Gating or Power Shutoff)

带状态保持功能的电源关断 (Power Gating with State Retention)

动态电压频率缩放 (Dynamic Voltage and Frequency Scaling)

自适应电压频率缩放 (Adaptive Voltage and Frequency Scaling )

低电压待机 (Low-Vdd Standby) 等

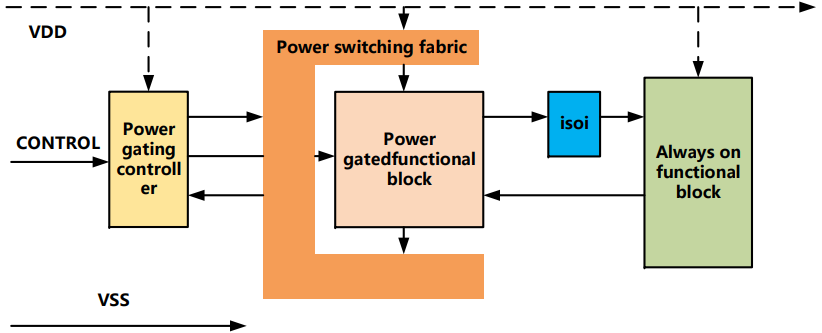

门控电源

芯片中某些模块不工作时,可以关断其电源,在需要工作时再将其电源导通,可以使电源关断区域的漏电流降至接近零,极大减少芯片的静态功耗。

- 片外关断:在芯片外部通过切断电源来关断芯片内部的某些模块

- 片内关断:分为精细关断和粗糙关断,精细关断需要特别库的支持,可实现每个标准单元的精细关断;而粗糙关断只需要一些门控单元就可以实现对某些模块的电源或地的控制

带有电源门控的SoC框图

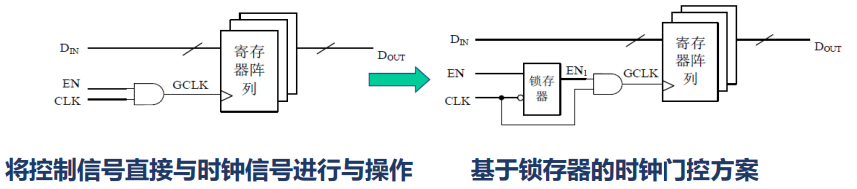

门控时钟

Latch在CLK为低时透明,EN1的毛刺仅出现在CLK的低电平处,此时将CLK与EN1相与则可消除

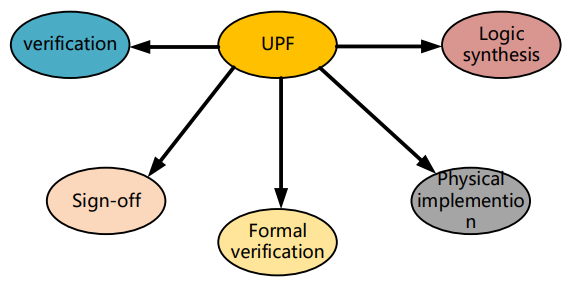

基于UPF的低功耗设计流程

统一的UPF文件,逻辑综合、物理实现、仿真验证、等效性检查以及signoff流程可按照UPF中对低功耗设计意图描述来完成整个IC设计实现验证流程。贯穿于整个流程的低功耗意图来源于同一个文件,大大降低低功耗设计的风险性。